1. 폰 노이만 구조(Von Neumann architecture)

폰 노이만 구조는 프로그램 내장 방식이라고도 불리며, 최초의 프로그램이 내장된 컴퓨터 구조로, 현재 모든 범용 컴퓨터들이 기본 설계로 따르고 있는 구조이다.

폰 노이만 구조는 연산의 수행과 관련된 명령어와 데이터를 메모리에 보관하게 되며, 순차적으로 메모리에 저장된 내용을 가져와서 지시대로 연산을 수행하는 방식이다.

1.1 장점

이전에 하드웨어 전선을 일일이 재배치하여 작업을 수행했던 것과 달리 폰 노이만 구조에서는 소프트웨어만 교체하면 되기 때문에 편의성과 범용성이 크게향상 되었다.

1.2 단점

폰 노이만 병목 현상이라는 문제가 존재한다. 폰 노이만 병목 현상은 CPU의 처리속도와 저장장치의 속도가 다를 때 나타나는 현상으로 CPU의 처리속도보다 기억장치의 속도가 느려 전체적으로 속도가 느려지는 현상을 말한다.

2. 컴퓨터 구조

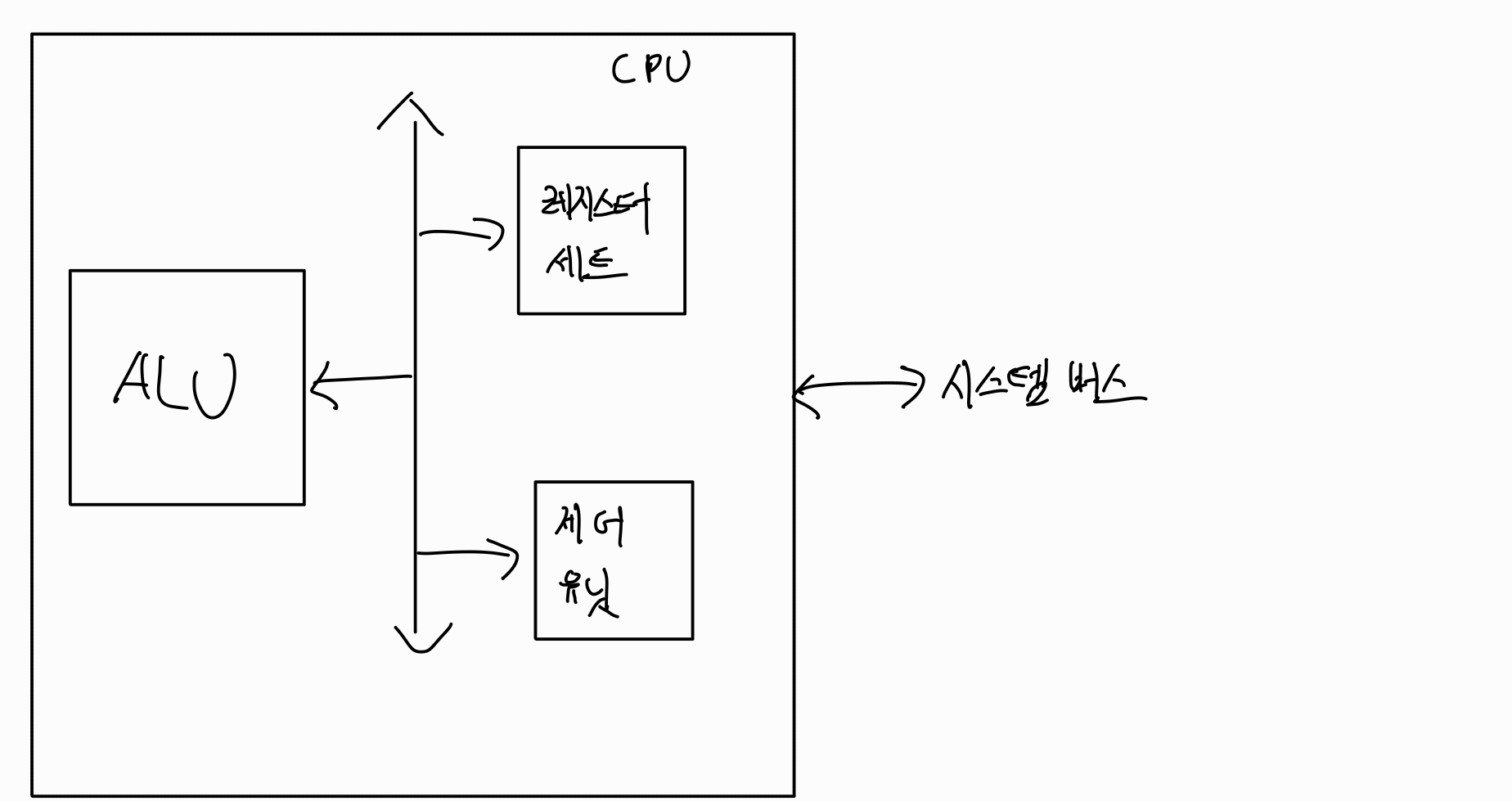

컴퓨터의 기본 구조는 위와 같으며 크게 4가지로 눠서 볼 수 있으며 각각 다음과 같은 역할을 수행한다.

- CPU(중앙처리장치): 프로그램 실행과 데이터 처리를 담당하는 중추적인 기능을 수행

- Memory(기억장치): 데이터를 저장하는 역할을 수행

- I/O(입출력 장치): 컴퓨터와 외부장치 사이에 데이터를 교환하는 역할을 수행

- System Bus(시스템 버스): CPU와 시스템 내의 다른 요소들 사이에 정보를 교환하는 통로의 역할을 수행

2.1 CPU

CPU의 구성요소

CPU는 명령을 해석하고, 명령 실행을 위한 제어신호를 발생시키는 CU(Control Unit), 산술, 논리 연산을 담당하는 ALU(Ariethematic Logic Unit), 레지스터 세트로 구성돼 있다.

CPU의 연산

1. Fetch(인출) : 메모리상의 프로그램 카운터(PC)가 가리키는 명령어를 CPU로 인출하여 적재한다.

2. Decode(해석) : 명령어를 해석한다. 이 단계에서 명령어의 종류와 타겟 등을 판단한다.

3. Execute(실행) : 해석된 명령어에 따라 데이터에 대한 연산을 수행한다.

4. Writeback(쓰기) : 명령어대로 처리 완료된 데이터를 메모리에 기록한다.

명령어 실행

CPU가 한 개의 명령어를 실행하는 데 필요한 전체 과정을 명령어 사이클이라고 부른다. 그리고 명령어 사이클은 CPU가 기억장치로부터 명령어를 읽어오는 명령어 인출단계와 인출된 명령어를 실행하는 명령어 실행단계로 이루어진다.

명렁어를 실행 시키기 위해 기본적으로 필요한 CPU 내부 레지스터들은 다음과 같다.

- 프로그램 카운터 PC: 다음에 인출될 명령어의 주소를 가지고 있는 레지스터이다. 각 명령어가 인출된 후에는 그 내용이 자동적으로 1 증가되며, 분기 명령어가 실행되는 경우에는 그 목적지 주소로 갱신된다.

- 누산기 AC: 데이터를 일시적으로 저장하는 레지스터이다.

- 명령어 레지스터 IR: 가장 최근에 인출된 명령어가 저장되어 있는 레지스터이다.

- 기억장치 주소 레지스터 MAR: PC에 저장된 명령어 주소가 시스템 주소 버스로 출력되기 전에 일시적으로 저장되는 주소 레지스터이다.

- 기억장치 버퍼 레지스터 MBR: 기기억장치에 저장될 데이터 혹은 기억장치로부터 읽혀진 데이터가 일시적으로 저장되는 버퍼 레지스터이다.

인출 사이클에서 CPU의 동작 과정

명령어 형식

명령어의 기본 요소를 나열하면 다음과 같다.

- 연산 코드: LOAD, ADD와 같이 수행할 연산을 지정해준다.

- 오퍼랜드: 연산을 수행하는데 필요한 데이터 혹은 데이터의 주소를 나타낸다.

- 다음 명령어의 주소: 현재의 명령어 실행이 완료된 후에 다음 명령어를 인출할 위치를 나타낸다. 분기 혹은 호출 명령어와 같이 실행 순서를 변경하는 경우에만 필요하다.

2.2 메모리

메모리는 RAM(Random Acess Memory)와 ROM(Read Only Memory)로 나뉘며 RAM은 다시 DRAM(Dynamic RAM)과 SRAM(Static RAM)으로 나뉜다.

DRAM은 SRAM에 비해 느리지만 저렴하기 떄문에 주기억장치로 사용되고 SRAM은 캐시 메모리 등에 사용된다.

ROM은 읽기만이 가능한 메모리로 컴퓨터 부팅을 위한 BIOS등에 사용된다.

2.3 버스

CPU, 메모리, 입출력 장치들의 자료교환을 위한 통로로 사용되며 한 번에 하나의 장치만이 버스에 접근 가능하다.

'.study > pwnable' 카테고리의 다른 글

| [포너블 기초] 함수 호출 규약 (0) | 2023.09.14 |

|---|---|

| [포너블 기초] Docker (0) | 2023.09.13 |

| [포너블 기초] 스택 프레임 (0) | 2023.09.12 |

| [포너블 기초] x86-32, x86-64 레지스터 (0) | 2023.09.12 |

| [포너블 기초] 메모리 구조 (0) | 2023.09.11 |